El Camino de Datos Multiciclo en el MIPS

En artículos anteriores le echamos un vistazo al funcionamiento del camino de datos del MIPS en Monociclo, ahora nos toca mirar el Multiciclo.

Monociclo VS Multiciclo

La principal diferencia que hay entre el camino de datos Monociclo y el Multiciclo es que en Monociclo una instrucción se ejecuta en un solo ciclo, tal y como indica su nombre, mientras que en Multiciclo una instrucción se puede realizar en varios ciclos. Esto implica que los problemas que nos podemos encontrar con este tipo de procesadores sean algo más complejos, por lo que se recomienda, en caso de hacerlos en papel, utilizar bolis de diferentes colores para identificar cada ciclo o utilizar un ordenador o tablet ya que en caso de cometer algún error durante la resolución puede ser muy engorroso indicarlo.

Por otro lado, el diagrama que utilizaremos será algo diferente al utilizado para monociclo, el que utilizábamos hasta ahora era este:

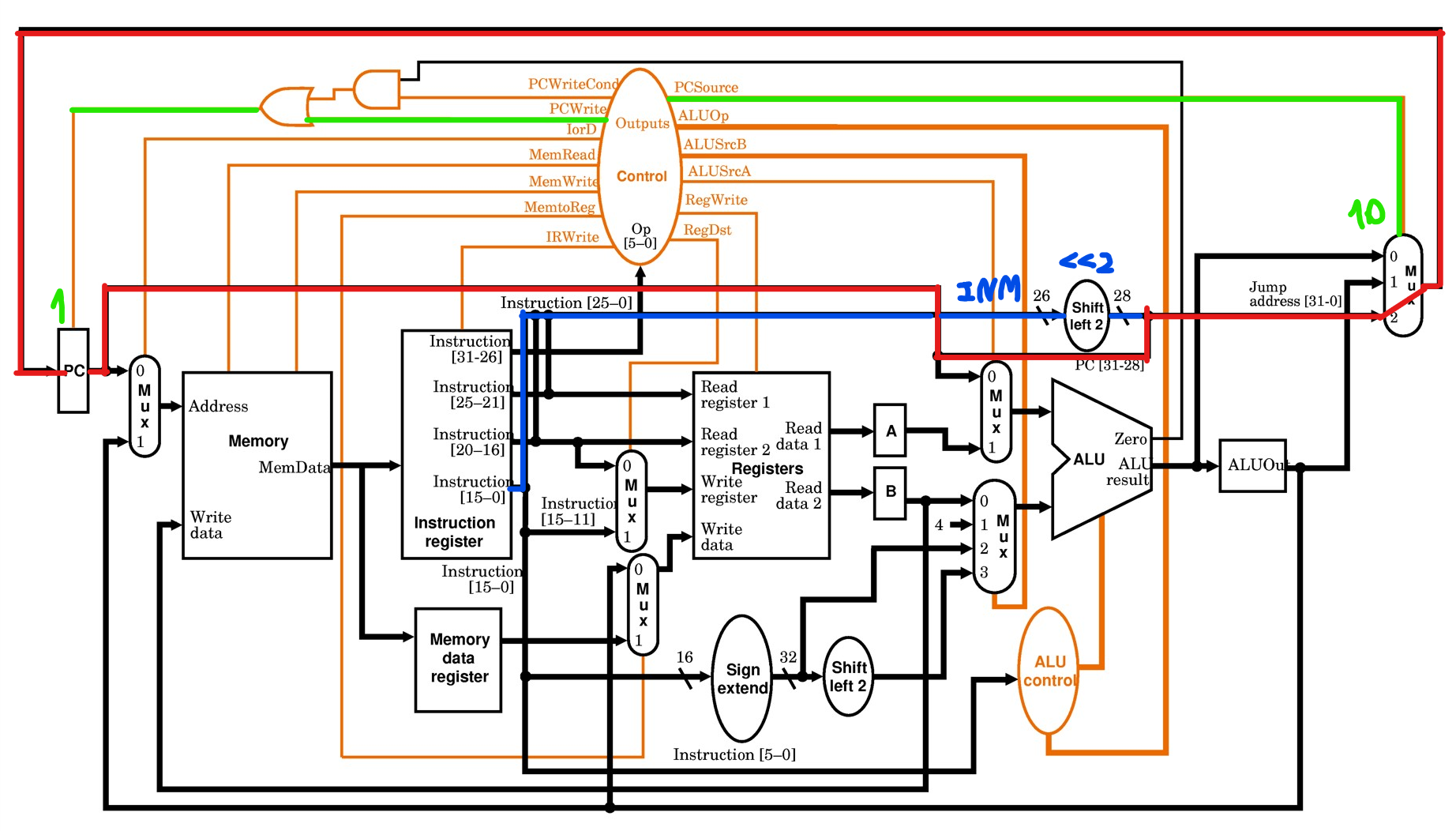

El diagrama que utilizaremos a partir de ahora para el camino de datos es el siguiente:

Este diagrama de buenas a primeras puede parecer mucho más complejo que el anterior, pero en realidad no es tan diferente, uno de los principales cambios es que ahora tenemos un nuevo componente llamado control del cual salen las señales de control para los diferentes elementos que nos encontramos en el procesador. Por otro lado podemos ver que de la ALU sale un cable que entra en ALUout y en un multiplexor que hay un poco más arriba en el diagrama, esto es para poder volver al inicio y hacer más operaciones en el siguiente ciclo.

El elemento CONTROL y las diferentes señales de control

Como dice el nombre de este componente, este se encarga de controlar que hace cada componente del procesador con las diferentes señales de salida que tiene. Estas señales de salida deben ser indicadas en cada ciclo que ejecutemos a la hora de realizar un problema de multiciclo. A continuación echaremos un vistazo a cuales son las señales de control más importantes:

PCWrite

Cuando vale 1, esta señal indica que queremos guardar el valor que entra en PC. En caso de valer 0 no se guarda nada en PC, podemos verla marcada en verde en el siguiente diagrama:

IorD

Indica si vamos a mandar a memoria una Instrucción o Datos (Instruction or Data), indica la entrada que recibirá la memoria, podemos ver esta señal marcada en verde en el siguiente diagrama:

MemRead y MemWrite

Estas 2 señales de control indican si vamos a escribir en memoria, en caso de valer 1 indicamos que estamos leyendo de memoria y/o guardando algo en esta, por ejemplo, si entra algo por WriteData y lo queremos guardar, ponemos MemWrite a 1 y si queremos leer algo de Address, ponemos MemRead a 1. Podemos ver esta señales de color verde en el siguiente diagrama:

MemtoReg

Esta señal de control indica que datos entrarán por WriteData al Registro, si vale 1 entrará información del Memory Data Register y en caso de valer 0 entrarán los datos de salida de la ALU. Podemos ver esta señal en verde en el siguiente diagrama:

Esta señal indica que se le va a mandar como entrada al PC para el siguiente ciclo, si esta señal vale 00 recibirá la salida de la ALU, si vale 01, recibirá la salida de ALUout como entrada y en caso de valer 10 recibirá una señal de salto. Podemos ver la señal en verde en el siguiente diagrama:

ALUOp

Indica que operación realizará la ALU. Si queremos sumar, ALUOp valdrá 00, en caso de querer restar 01, 10 para operaciones en instrucciones de tipo R. Podemos ver esta señal en verde en el siguiente diagrama:

ALUSrcA

Esta señal indica cual va a ser la entrada A de la ALU, si el valor de esta señal de control es 0 entra el PC a la ALU en caso de que valga 1 entrará el dato de la salida Read Data 1 del Registro. Podemos ver la señal en cuestión de color verde en el siguiente diagrama:

ALUSrcB

Esta señal indica cual será el valor de la entrada B de la ALU. En caso de valer 00 recibirá como entrada el valor de la salida Read Data 2 del Registro, si vale 01 recibirá un 4 (Esto se suele utilizar para el PC+4), en caso de valer 10 recibirá la salida Instruction[0-15] extendida a 32 Bits y en caso de ser 11 recibirá la misma señal pero corrida 2 bits a la izquierda. Podemos ver esta señal en verde en el siguiente diagrama:

RegWrite

Esta señal le indica al registro que queremos almacenar el valor que entra por Write Data en la dirección indicada por la entrada Write Register. Si vale 1 indicamos que queremos realizar el guardado, en caso de valer 0 no se guardará nada en el Registro. Podemos ver la señal en el siguiente diagrama de color verde:

RegDest

Esta señal indica la ubicación en la que queremos almacenar en el registro un dato que entre por WriteData, si vale 0 se almacenará en en la ubicación que se encuentra en la salida del Registro de Instrucciones Instruction[20-16], mientras que en caso de valer 1 se almacenará en Instruction[15-11]. Podemos ver la señal de control en el siguiente diagrama en color verde:

Etapas

Una de las ventajas del Multiciclo es que podemos ejecutar una instrucción en varios ciclos, normalmente estos ciclos se dividen en varias etapas para localizar la instrucción, decodificarla, ejecutarla, acceder a memoria y almacenar los datos resultantes de la operación, estas etapas son las siguientes:

Etapa 1: Búsqueda de Instrucción (IF: Instruction Fetch)

En esta etapa lo que se hace es cargar en el Registro de Instrucciones el PC y, simultáneamente, cargar PC+4 en el PC, esta etapa se debe ejecutar siempre como primera etapa, las señales de control de esta serían las siguientes:

| Etapa 1 Operaciones: IR = Mem[PC] y PC = PC + 4 |

| Señal de Control |

Valor |

| IorD |

0 |

| MemRead |

1 |

| MemWrite |

0 |

A continuación podemos ver en verde las señales de control y en rojo el camino de datos:

Etapa 2: Etapa de Decodificación (ID: Instruction Decodification)

Esta segunda etapa, al igual que la de Búsqueda de Instrucción, ocurre siempre como segunda etapa. Lo que hacemos es cargar los datos que se encuentran en la posiciones Instruction[25-21] e Instruction[20-16] del Registro como las entradas A y B de la ALU respectivamente. La el valor de ALUout será el del PC sumado al de Instruction[15-0] del Register con el signo extendido y corrido 2 posiciones a la izquierda (A esto le llamaremos Valor Inmediato con el Signo Extendido << 2). Las señales de control serán las siguientes:

Etapa 2 Operaciones:

A = Reg[IR(25-21)] y B = [IR(20-16)] ALUOut = PC + INM.SigExt<<2 |

| Señal de Control |

Valor |

| ALUOp |

00 |

| ALUSrcA |

0 |

| ALUSrcB |

11 |

A continuación podemos ver en verde las señales de control y en rojo el camino de datos:

Etapa 3: Ejecución (EX)

En esta fase se ejecutan las operaciones de la instrucción, dependiendo de la instrucción que estemos ejecutando esta etapa puede variar mucho, por eso vamos a poner varios ejemplos de como iría esta etapa:

Ejecución Instrucciones de Tipo R

En las instrucciones de Tipo R solemos utilizar las siguientes Señales de control:

| Etapa 3 Ejecución Tipo R |

| Señal de Control |

Valor |

| ALUSrcA |

1 |

| ALUSrcB |

00 |

| ALUOP |

10 |

Ejecución SW y LW

Para realizar un store Word utilizaremos las siguientes señales de control :

Etapa 3 Ejecución SW

ALUout = A+INM.SigExt y B = Reg[IR(20-16)] |

| Señal de Control |

Valor |

| ALUSrcA |

1 |

| ALUSrcB |

10 |

| ALUOP |

00 |

El camino de datos (Rojo) y las señales de control (Verde) serían las siguientes:

Ejecución BeQ

Etapa 3 Ejecución BeQ

ALUout = A-B y PC = ALUOut |

| Señal de Control |

Valor |

| ALUSrcA |

1 |

| ALUSrcB |

00 |

| ALUOP |

01 |

| PCWrite |

1 |

| PCSrc |

01 |

El camino de datos (Rojo) y las señales de control (Verde) serían las siguientes:

Ejecución J

Etapa 3 Ejecución J

PC=[31-28]PC || INM<<2 |

| Señal de Control |

Valor |

| PCSrc |

10 |

| PCWrite |

1 |

A continuación podemos ver el camino de datos (En rojo y Azul) y las señales de control (Verde)

Etapa 4: Acceso a Memoria (MEM)

En esta etapa las instrucciones de salto como J y BeQ no se utilizarán al haber realizado su función de salto ya en la etapa de Ejecución.

Acceso a Memoria Tipo R

Etapa 4 Acceso a Memoria Tipo R

Reg[IR(15-11)]=ALUOut |

| Señal de Control |

Valor |

| MemToReg |

0 |

| RegDest |

1 |

| RegWrite |

1 |

El camino de datos (Rojo) y las señales de control serían las siguientes:

Acceso a Memoria LW

Etapa 4 Acceso a Memoria LW

MDR = Mem[ALUOut] |

| Señal de Control |

Valor |

| IorD |

1 |

| MemRead |

1 |

El camino de datos (Rojo) y las señales de control serían las siguientes:

Acceso a Memoria SW

Etapa 4 Acceso a Memoria SW

Mem[ALUOut]=B |

| Señal de Control |

Valor |

| IorD |

1 |

| MemWrite |

1 |

El camino de datos (Rojo) y las señales de control serían las siguientes:

Etapa 5: Post Escritura (WB)

Esta etapa generalmente solo se aplica a LW

Etapa 5 PostEscritura LW

Reg[IR(20-16)]=MDR |

| Señal de Control |

Valor |

| MemToReg |

1 |

| RegDest |

0 |

| RegWrite |

1 |

El camino de datos (Rojo) y las señales de control serían las siguientes:

0 Comentarios